This data sheet contains advance information and specifications are subject to change without notice.

# EUROM 60 Hz

#### GENERAL DESCRIPTION

The SAA5361 EUROM is a single-chip VLSI NMOS crt controller capable of handling all display functions required by the CEPT videotex terminal, model A4. Only minimal hardware is required to produce a videotex terminal using EUROM — the simplest configuration needs just a microcontroller and 4 Kbytes of display memory.

#### **Features**

- Minimal additional hardware required

- Screen formats of 40/80 character by 1-to-25 row display

- 512 alphanumeric or graphical characters on-chip or extendable off-chip

- Serial attribute storage (STACK) and parallel attribute storage

- Dynamically redefinable character (DRCS) capability over full field

- Interfaces with 8/16-bit microprocessors with optional direct memory access

- On-chip scroll map minimizes data to be transferred when scrolling

- On-chip colour map RAM (4096 locations) and three on-chip digital-to-analogue converters allow 32 colours on-screen

- On-chip digital-to-analogue converters are non-linear to compensate for crt non-linearity

- Memory interface capable of supporting multi-page terminals. EUROM can access up to 128 Kbytes of display memory

- Programmable cursor

- Programmable local status row

- Three synchronization modes:

stand-alone

built-in oscillator operating with an external 7.2 MHz crystal

simple slave phase-locked slave directly synchronized from the source of text composite sync indirect synchronization allows picture-in-text displays (e.g. VCR/VLP video

with text overlay)

- On-chip timing composite sync output

- Zoom feature which allows the height of any group of rows to be increased to enhance legibility

# **PACKAGE OUTLINE**

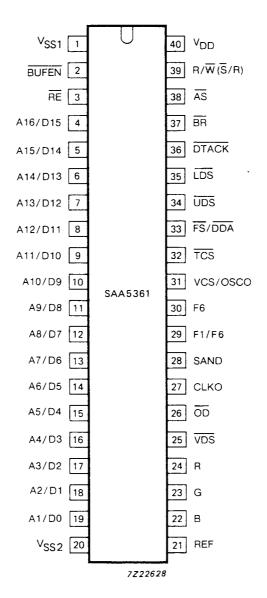

40-lead DIL; plastic (SOT129).

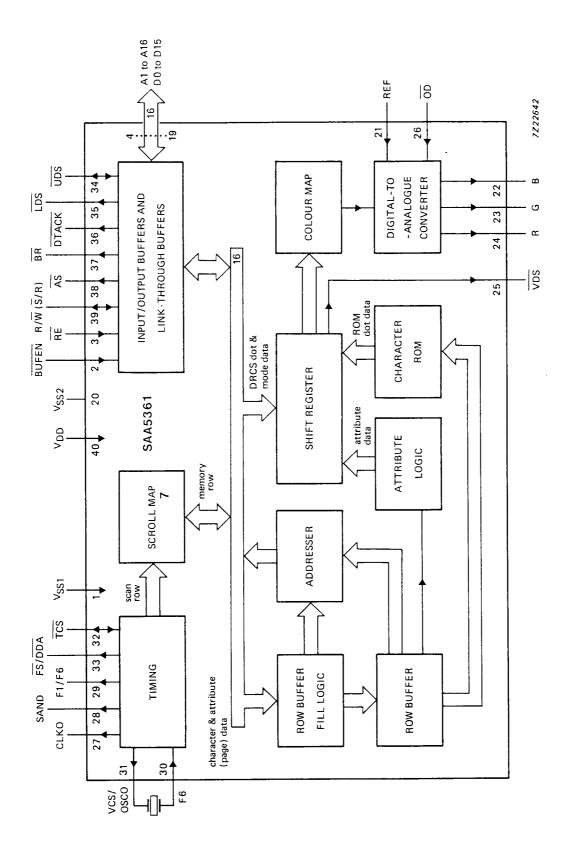

Fig. 1 Block diagram.

|                  | PINNIN         | G                       |                                                                                                                                                                                                                                                                               |  |

|------------------|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  | 1              | V <sub>SS1</sub>        | Ground 0 V.                                                                                                                                                                                                                                                                   |  |

|                  | 2              | BUFEN                   | Buffer enable input to the 8-bit link-through buffer.                                                                                                                                                                                                                         |  |

|                  | 3              | RE                      | Register enable input. This enables A1 to A6 and $\overline{\text{UDS}}$ as inputs, and D8 to D15 as input/outputs.                                                                                                                                                           |  |

|                  | 4 to 19        | A16 to A1/<br>D15 to D0 | Multiplexed address and data bus input/outputs. These pins also function as the 8-bit link-through buffer.                                                                                                                                                                    |  |

|                  | 20             | V <sub>SS2</sub>        | Ground (0 V).                                                                                                                                                                                                                                                                 |  |

|                  | 21             | REF                     | Analogue reference input.                                                                                                                                                                                                                                                     |  |

|                  | 22<br>23<br>24 | B<br>G<br>R             | Analogue outputs (signals are gamma-corrected).                                                                                                                                                                                                                               |  |

|                  | 25             | VDS                     | Switching output for dot, screen (row), box and window video data; for use when video signal is present (e.g. from tv, VLP, alpha + photographic layer). This output is LOW for tv display and HIGH for text and will interface directly with a number of colour decoder ICs. |  |

| DATA             | 26             | ŌD                      | Output disable causing R, G, B and $\overline{\text{VDS}}$ outputs to go to high-impedance state. Can be used at dot-rate.                                                                                                                                                    |  |

|                  | 27             | CLKO                    | 14.4 MHz clock output for hard-copy dot synchronization (referenced to output dots).                                                                                                                                                                                          |  |

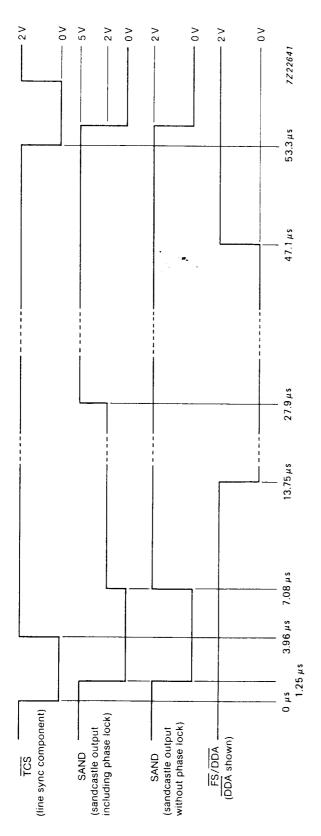

| /ENT             | 28             | SAND                    | Sandcastle feedback to other circuit, when display must be locked to a VLP. The phase-lock part of the sandcastle waveform can be disabled.                                                                                                                                   |  |

| DEVELOPMENT DATA | 29             | F1/F6                   | 1.2 MHz or 7.2 MHz output.                                                                                                                                                                                                                                                    |  |

|                  | 30             | F6                      | 7.2 MHz clock input. Internal AC coupling is provided.                                                                                                                                                                                                                        |  |

| DEV              | 31             | VCS/OSCO                | Video composite sync input for phase reference of vertical display timing when locking to a video source or, in stand-alone sync mode, output from internal oscillator circuit (fixed frequency).                                                                             |  |

|                  | 32             | TCS                     | Text composite sync input/output depending on master/slave status.                                                                                                                                                                                                            |  |

|                  | 33             | FS/DDA                  | Field sync pulse output or defined-display-area flag output (both referenced to output dots).                                                                                                                                                                                 |  |

|                  | 34             | UDS                     | Upper data strobe input/output.                                                                                                                                                                                                                                               |  |

|                  | 35             | LDS                     | Lower data strobe output.                                                                                                                                                                                                                                                     |  |

|                  | 36             | DTACK                   | Data transfer acknowledge (open drain output).                                                                                                                                                                                                                                |  |

|                  | 37             | BR                      | Bus request to microprocessor (open drain output).                                                                                                                                                                                                                            |  |

|                  | 38             | ĀS                      | Address strobe output to external address latches.                                                                                                                                                                                                                            |  |

|                  | 39             | R/W (S/R)               | Read/write input/output. Also serves as send/receive for the link-through buffer.                                                                                                                                                                                             |  |

|                  | 40             | $V_{DD}$                | Positive supply voltage (+ 5 V).                                                                                                                                                                                                                                              |  |

# PINNING (continued)

Fig. 2 Pinning diagram.

# **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage range (pin 40)               | $v_DD$            | -0.3 to $+7.5$ V  |

|---------------------------------------------|-------------------|-------------------|

| Maximum input voltage (except F6, TCS, REF) | $v_{Imax}$        | -0.3 to $+7.5$ V  |

| Maximum input voltage (F6, TCS)             | V <sub>Imax</sub> | -0.3 to $+10.0$ V |

| Maximum input voltage (REF)                 | $v_{REF}$         | -0.3  to  +3.0  V |

| Maximum output voltage                      | $v_{\sf Omax}$    | -0.3  to + 7.5  V |

| Maximum output current                      | lOmax             | 10 mA             |

| Operating ambient temperature range         | $T_{amb}$         | 0 to +60 °C       |

| Storage temperature range                   | $T_{stg}$         | -55 to + 125 °C   |

Outputs other than CLKO, OSCO, R, G, B, and  $\overline{\text{VDS}}$  are short-circuit protected.

# **CHARACTERISTICS**

$V_{DD}$  = 5 V ± 5%;  $V_{SS}$  = 0 V;  $T_{amb}$  = 0 to +60 °C, unless otherwise specified

| parameter                                                                                           | symbol               | min. | typ.   | max. | unit |

|-----------------------------------------------------------------------------------------------------|----------------------|------|--------|------|------|

| SUPPLY                                                                                              |                      |      |        |      |      |

| Supply voltage (pin 40)                                                                             | $V_{DD}$             | 4.75 | 5.0    | 5.25 | V    |

| Supply current (pin 40)                                                                             | <sup>1</sup> DD      | -    | -      | 390  | mA   |

| INPUTS                                                                                              |                      |      |        |      |      |

| F6                                                                                                  |                      |      |        |      |      |

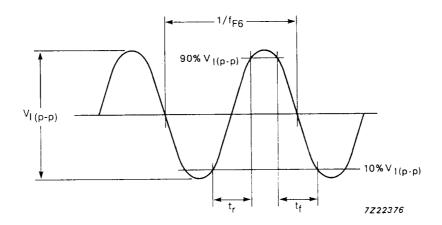

| Slave modes (Fig. 3)                                                                                |                      |      |        |      |      |

| Input voltage (peak-to-peak value)                                                                  | V <sub>1 (p-p)</sub> | 2.5  | 3.0    | 7.0  | V    |

| Input leakage current at V <sub>I</sub> = 0 to V <sub>CC max</sub> ; T <sub>amb</sub> = 25 °C       | 161                  | _    | _      | 20   | μΑ   |

| Input capacitance                                                                                   | CI                   | _    | -      | 12   | рF   |

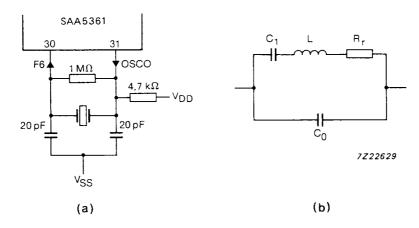

| Stand-alone mode (Fig. 4)                                                                           |                      |      |        |      |      |

| Series capacitance of crystal                                                                       | C <sub>1</sub>       | -    | 28     | _    | fF   |

| Parallel capacitance of crystal                                                                     | c <sub>0</sub>       | -    | 7.1    | _    | pF   |

| Resonance resistance of crystal                                                                     | R <sub>r</sub>       | -    | -      | 60   | Ω    |

| BUFEN, RE, OD                                                                                       |                      |      |        |      |      |

| Input voltage LOW                                                                                   | ∨ <sub>IL</sub>      | 0    | _      | 0.8  | V    |

| Input voltage HIGH                                                                                  | ∨ <sub>IH</sub>      | 2.0  | _      | 6.5  | V    |

| Input leakage current at $V_1 = 0$ to $V_{DD} + 0.3 \text{ V}$ ; $T_{amb} = 25  {}^{\circ}\text{C}$ | 116                  | -10  | _      | + 10 | μΑ   |

| Input capacitance                                                                                   | C <sub>1</sub>       | _    | -      | 7    | pF   |

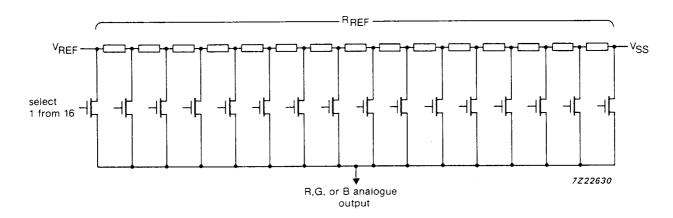

| REF (Fig. 5)                                                                                        |                      |      |        |      |      |

| Input voltage                                                                                       | VREF                 | 0    | 1 to 2 | 2.7  | V    |

| Resistance (pin 21 to pin 20) with REF supply and R, G, B outputs OFF                               | R <sub>REF</sub>     | _    | 125    | _    | Ω    |

# **CHARACTERISTICS** (continued)

| parameter                                                                                                                 | symbol                                | min. | typ. | max.            | unit |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|-----------------|------|

| OUTPUTS                                                                                                                   |                                       |      |      |                 |      |

| SAND                                                                                                                      |                                       |      |      |                 |      |

| Output voltage high level at $I_O = 0$ to $-10 \mu A$                                                                     | V <sub>OH</sub>                       | 4.2  | _    | V <sub>DD</sub> | V    |

| Output voltage intermediate level at $I_O = -10$ to $+ 10 \mu A$                                                          | VOI                                   | 1.3  | _    | 2.7             | V    |

| Output voltage low level at $I_0 = 0.2 \text{mA}$                                                                         | VOL                                   | 0    | _    | 0.2             | V    |

| Load capacitance (note 1)                                                                                                 | CL                                    | -    | -    | 130             | pF   |

| F1/F6, DDA/FS                                                                                                             |                                       |      |      |                 |      |

| Output voltage HIGH                                                                                                       | Voн                                   | 2.4  | -    | $V_{DD}$        | V    |

| Output voltage LOW at $I_{OL} = 3.2 \text{ mA}$                                                                           | VOL                                   | 0    | -    | 0.4             | V    |

| Load capacitance (note 1)                                                                                                 | CL                                    | -    | -    | 50              | pF   |

| LDS, AS                                                                                                                   |                                       |      |      |                 |      |

| Output voltage HIGH at                                                                                                    |                                       |      |      | ·               |      |

| I <sub>OH</sub> = -200 μA                                                                                                 | Vон                                   | 2.0  | -    | VDD             | V    |

| Output voltage LOW at $I_{OL} = 3.2 \text{ mA}$                                                                           | VOL                                   | 0    | -    | 0.8             | V    |

| Load capacitance (note 1)                                                                                                 | CL                                    | -    | -    | 200             | pF   |

| DTACK, BR (open drain outputs)                                                                                            |                                       |      |      |                 |      |

| Output voltage LOW at IOL = 3.2 mA                                                                                        | VOL                                   | 0    | -    | 0.4             | V    |

| Load capacitance (note 1)                                                                                                 | CL                                    | _    | _    | 150             | рF   |

| Capacitance (OFF state)                                                                                                   | COFF                                  | -    | -    | 7               | pF   |

| R, G, B (note 2)                                                                                                          |                                       |      |      |                 |      |

| Output voltage HIGH (note 3) at $I_{OH} = -100 \mu A$ ; $V_{REF} = 2.7 V$                                                 | V <sub>OH</sub>                       | 2.4  | _    |                 | V    |

| Output voltage LOW at $I_{OL} = 2 \text{ mA}$ (note 10)                                                                   | VOL                                   | -    | _    | 0.4             | V    |

| Output resistance during line blanking                                                                                    | ROBL                                  | -    | _    | 150             | Ω    |

| Output capacitance (OFF state)                                                                                            | COFF                                  | _    | -    | 12              | pF   |

| Output leakage current (OFF state) at V <sub>I</sub> = 0 to V <sub>DD</sub> + 0.3 V; T <sub>amb</sub> = 25 <sup>o</sup> C | OFF                                   | -10  |      | + 10            | μΑ   |

| CLOCKO                                                                                                                    |                                       |      |      |                 |      |

|                                                                                                                           | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |      |      |                 |      |

| Output voltage HIGH                                                                                                       | Voн                                   | 2.0  |      | V <sub>DD</sub> | V    |

| Output voltage LOW                                                                                                        | VOL                                   | 0    |      | 0.8             | V    |

| Load capacitance (note 1)                                                                                                 | CL                                    | -    |      | 50              | pF   |

| parameter                                                                                                                     | symbol                               | min.          | typ.        | max.                          | unit           |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|-------------|-------------------------------|----------------|

| VDS                                                                                                                           |                                      |               |             |                               |                |

| Output voltage HIGH Output voltage LOW Output leakage current (OFF state)                                                     | VOH<br>VOL                           | 2.0<br>0      | _<br>_      | V <sub>DD</sub><br>0.8        | V              |

| at V <sub>I</sub> = 0 to V <sub>DD</sub> + 0.3 V;<br>T <sub>amb</sub> = 25 °C                                                 | LO                                   | 10            | _           | + 10                          | μΑ             |

| INPUTS/OUTPUTS                                                                                                                |                                      |               |             |                               |                |

| VCS/OSCO                                                                                                                      |                                      |               |             |                               |                |

| Input voltage HIGH Input voltage LOW Output leakage current (output OFF) at                                                   | V <sub>I</sub> H<br>V <sub>I</sub> L | 2.0           |             | 6.0<br>0.8                    | V<br>V         |

| V <sub>I</sub> = 0 to V <sub>DD</sub> + 0.3 V;<br>T <sub>amb</sub> = 25 °C<br>Input capacitance<br>Load capacitance (note 1)  | ILO<br>CL                            | -10<br>-<br>- | _<br>_<br>_ | + 10<br>10<br>50              | μΑ<br>pF<br>pF |

| TCS                                                                                                                           | <b>–</b>                             |               |             |                               |                |

| Input voltage HIGH<br>Input voltage LOW<br>Output leakage current at                                                          | V <sub>I</sub> H<br>V <sub>I</sub> L | 3.5<br>0      |             | 10.0<br>1.5                   | V<br>V         |

| $V_1 = 0$ to $V_{DD} + 0.3$ V;<br>$T_{amb} = 25$ °C<br>Input capacitance                                                      | ILO<br>Cl                            | _10<br>_      |             | + 10<br>10                    | μA<br>pF       |

| Output voltage HIGH at $I_{OH} = -200$ to $100 \mu\text{A}$ Output voltage LOW at $V_{OL} = 3.2$ mA Load capacitance (note 1) | VOH<br>VOL<br>CL                     | 2.0<br>0<br>— | _<br>_<br>_ | 6.0<br>0.8<br>50              | V<br>V<br>pF   |

| A1/D0 to A16/D15                                                                                                              |                                      |               |             |                               |                |

| Input voltage LOW<br>Input voltage HIGH<br>Output leakage current                                                             | V <sub>I</sub> L<br>V <sub>I</sub> H | 0<br>2.0      |             | 0.8<br>6.0                    | V              |

| V <sub>I</sub> = 0 to V <sub>DD</sub> + 0.3 V;<br>T <sub>amb</sub> = 25 <sup>o</sup> C<br>Input capacitance                   | I <sub>LO</sub>                      | -10<br>-      | _           | + 10<br>10                    | μA<br>pF       |

| Output voltage HIGH at $I_{OH}$ = $-200 \mu A$<br>Output voltage LOW at $I_{OL}$ = 3.2 mA<br>Load capacitance (note 1)        | VOH<br>VOL<br>CL                     | 2.4<br>0<br>- |             | V <sub>DD</sub><br>0.4<br>200 | V<br>V<br>pF   |

| UDS; R/W                                                                                                                      |                                      |               |             |                               |                |

| Input voltage LOW Input voltage HIGH Output leakage current at                                                                | VIL                                  | 2.0           | _           | 0.8<br>6.0                    | V              |

| V <sub>I</sub> = 0 to V <sub>DD</sub> + 0.3 V;<br>T <sub>amb</sub> = 25 °C<br>Input capacitance<br>Output voltage HIGH        | LO<br>CIN                            | _10<br>_      |             | + 10<br>10                    | μA<br>pF       |

| (I <sub>OH</sub> = -200 μA) Output voltage LOW                                                                                | Voн                                  | 2.0           | _           | V <sub>DD</sub>               | \ \            |

| (I <sub>OH</sub> = 3.2 mA)<br>Load capacitance (note 1)                                                                       | V <sub>OL</sub>                      | 0 –           | -<br>  -    | 0.8<br>200                    | V<br>pF        |

# **CHARACTERISTICS** (continued)

| parameter                                                                    | symbol                            | min. | typ. | max. | unit |

|------------------------------------------------------------------------------|-----------------------------------|------|------|------|------|

| TIMING                                                                       |                                   |      |      |      |      |

| Values guaranteed at 0.8 V and 2.0 V levels<br>F6 input frequency at 7.2 MHz |                                   |      |      |      |      |

| <b>F6</b> (Fig. 3)                                                           |                                   |      |      |      |      |

| Rise and fall times                                                          | t <sub>r</sub> , t <sub>f</sub>   | 10   | -    | 69   | ns   |

| Frequency                                                                    | fF6                               | -    | 72   | _    | MHz  |

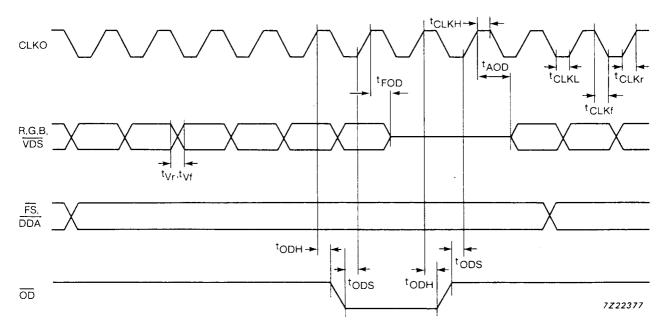

| CLKO, F1/F6, R, G, B, VDS, FS/DDA, OD (notes 4, 5 and Fig. 6)                |                                   |      |      |      |      |

| CLKO HIGH time                                                               | <sup>t</sup> CLKH                 | 20   | -    | -    | ns   |

| CLKO LOW time                                                                | t <sub>CLKL</sub>                 | 12   | -    | -    | ns   |

| CLKO rise and fall times                                                     | <sup>t</sup> CLKr                 | -    | _    | 10   | ns   |

|                                                                              | <sup>t</sup> CLKf                 | _    | -    | 10   | ns   |

| CLKO HIGH to R, G, B, $\overline{VDS}$ floating after $\overline{OD}$ fall   | t <sub>FOD</sub>                  | 0    | _    | 30   | ns   |

| Skew between outputs R, G, B, VDS                                            | tvs                               | _    | _    | 20   | ns   |

| R, G, B, VDS rise and fall times                                             | t <sub>Vr</sub> , t <sub>Vf</sub> | _    | _    | 30   | ns   |

| CLKO HIGH to R, G, B, VDS active                                             |                                   |      |      |      |      |

| after $\overline{\text{OD}}$ rise                                            | tAOD                              | 0    | -    | 60   | ns   |

| F1 HIGH time (note 5)                                                        | tF1H                              | 333  | 417  | 500  | ns   |

| F1 LOW time (note 5)                                                         | t <sub>F1L</sub>                  | 333  | 417  | 500  | ns   |

| F6 HIGH time                                                                 | <sup>t</sup> F6H                  | 33   | 69   | 100  | ns   |

| F6 LOW time                                                                  | <sup>t</sup> F6L                  | 33   | 69   | 100  | ns   |

| OD to CLKO rise set-up                                                       | tods                              | -    | -    | 45   | ns   |

| OD to CLKO HIGH hold                                                         | tODH                              | -    | -    | 0    | ns   |

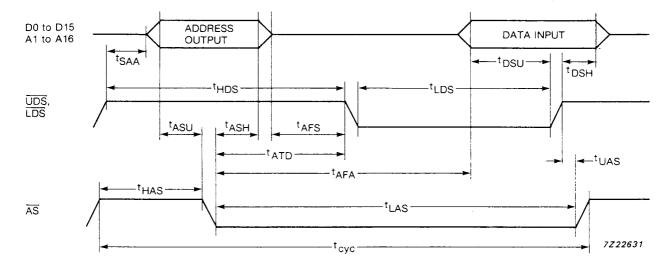

| MEMORY ACCESS TIMING                                                         |                                   |      |      |      |      |

| (notes 1, 6, 7 and Fig. 7)                                                   |                                   |      |      |      |      |

| UDS, LDS, AS                                                                 |                                   |      |      |      |      |

| Cycle time                                                                   | t <sub>cyc</sub>                  | _    | 417  | -    | ns   |

| UDS HIGH to bus-active for address output                                    | t <sub>SAA</sub>                  | 65   | _    | _    | ns   |

| Address valid set-up to AS fall                                              | t <sub>ASU</sub>                  | 16   | _    | _    | ns   |

| Address valid hold from $\overline{AS}\ LOW$                                 | t <sub>ASH</sub>                  | 16   | -    | _    | ns   |

| Address float to UDS fall                                                    | †AFS                              | 0    | _    | _    | ns   |

| parameter                                  | symbol           | min. | typ. | max.         | unit |

|--------------------------------------------|------------------|------|------|--------------|------|

| AS LOW to UDS fall delay                   | <sup>t</sup> ATD | 42   | _    | _            | ns   |

| UDS, LDS HIGH time                         | tHDS             | 180  | _    | _            | ns   |

| UDS, LDS LOW time (note 9)                 | tLDS             | 160  | _    | _            | ns   |

| AS HIGH time                               | tHAS             | 100  | _    | _            | ns   |

| AS LOW time                                | tLAS             | 240  | _    | _            | ns   |

| Data valid set-up to UDS rise              | tDSU             | 25   | - ·  | <del>-</del> | ns   |

| Data valid hold from UDS HIGH              | tDSH             | 10   | _    | _            | ns   |

| UDS HIGH to AS rise delay                  | tUAS             | 0    | _    | 15           | ns   |

| $\overline{AS}$ LOW to data valid          | <sup>t</sup> AFA | _    | _    | 225          | ns   |

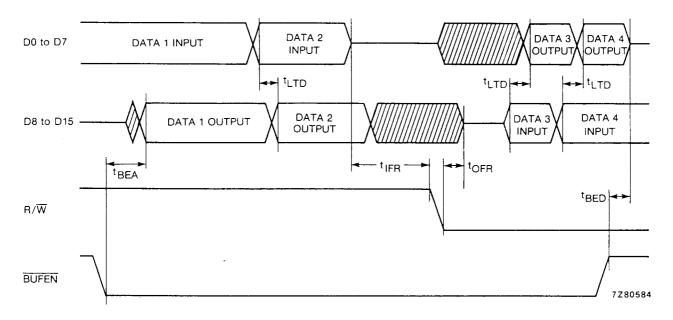

| Link-through buffers                       |                  |      |      |              |      |

| (notes 6, 7 and Fig. 8)                    |                  |      |      |              |      |

| BUFEN LOW to output valid                  | t <sub>BEA</sub> | -    | _    | 85           | ns   |

| Link-through delay time                    | <sup>t</sup> LTD | _    | _    | 70           | ns   |

| Input data float prior to direction change | tIFR             | 0    | _    | _            | ns   |

| Output float after direction change        | tOFR             | _    | _    | 50           | ns   |

| Output float after BUFEN HIGH              | <sup>t</sup> BED | _    | _    | 50           | ns   |

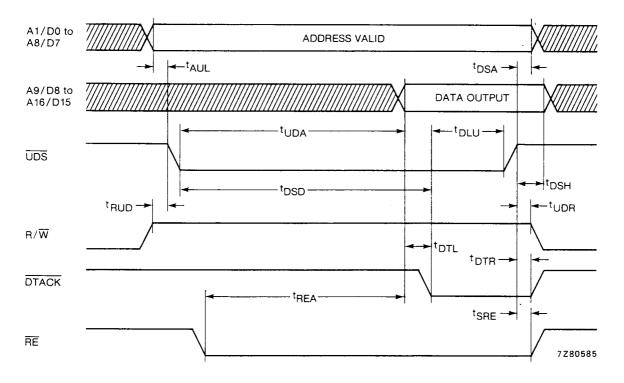

| Microprocessor READ from EUROM             |                  |      |      |              |      |

| (Fig. 9)                                   |                  |      |      |              |      |

| R/W HIGH set-up to UDS fall                | <sup>t</sup> RUD | 0    | _    | _            | ns   |

| UDS LOW to returned-data access time       | tUDA             | _    | _    | 210          | ns   |

| RE LOW to returned data access time        | †REA             | _    | _    | 210          | ns   |

| Data valid to DTACK LOW delay              | †DTL             | 0    | _    | _            | ns   |

| DTACK LOW to UDS rise                      | <sup>t</sup> DLU | 10   | _    | _            | ns   |

| UDS HIGH to DTACK rise                     | <sup>t</sup> DTR | 0    | _    | 50           | ns   |

| UDS HIGH to address hold                   | tDSA             | 10   | _    | _            | ns   |

| UDS HIGH to data hold                      | <sup>t</sup> DSH | 8    | _    | _            | ns   |

| UDS HIGH to RE rise                        | t <sub>SRE</sub> | 10   | _    | _            | ns   |

| ŪDS HIGH to R/₩ fall                       | tUDR             | 0    | _    | _            | ns   |

| UDS LOW to DTACK LOW                       | tDSD             | -    | _    | 260          | ns   |

| Address valid to UDS fall                  | <sup>t</sup> AUL | 0    |      |              | ns   |

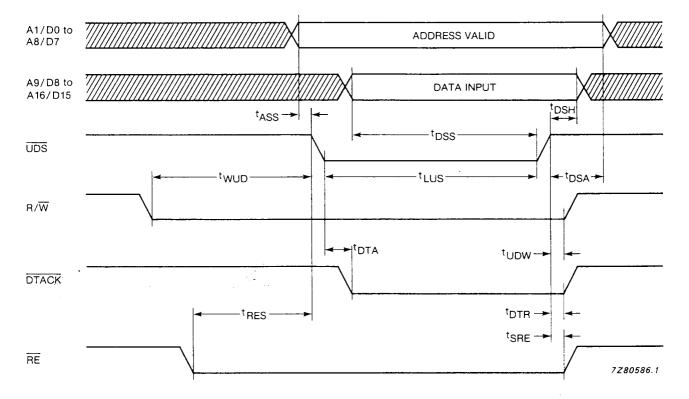

## **CHARACTERISTICS** (continued)

| parameter                                                                                                                                      | symbol           | min.     | typ.         | max.   | unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|--------------|--------|----------|

| MEMORY ACCESS TIMING (continued)  Microprocessor WRITE to EUROM (Fig. 10)                                                                      |                  |          |              |        |          |

| Write cycle time (note 8)                                                                                                                      | twcy             | 500      | _            | _      | ns       |

| R/W LOW set-up to UDS fall                                                                                                                     | twup             | 0        | _            | _      | ns       |

| RE LOW to UDS fall                                                                                                                             | tRES             | 30       | _            | -      | ns       |

| Address valid to UDS fall                                                                                                                      | tASS             | 30       | -            | _      | ns       |

| UDS LOW time                                                                                                                                   | tLUS             | 100      | _            |        | ns       |

| Data valid to UDS rise                                                                                                                         | tDSS             | 80       | _            | -      | ns       |

| UDS LOW to DTACK LOW                                                                                                                           | <sup>t</sup> DTA | 0        | -            | 60     | ns       |

| UDS HIGH to DTACK rise                                                                                                                         | t <sub>DTR</sub> | 0        | -            | 50     | ns       |

| UDS HIGH to data hold                                                                                                                          | tDSH             | 10       | -            | _      | ns       |

| UDS HIGH to address hold                                                                                                                       | tDSA             | 10       | -            | -      | ns       |

| UDS HIGH to RE rise                                                                                                                            | tSRE             | 10       | -            | _      | ns       |

| UDS HIGH to R/W rise                                                                                                                           | tuDW             | 0        | -            | _      | ns       |

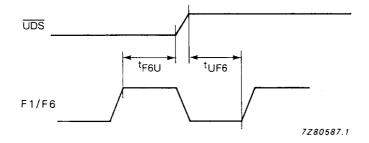

| F1/F6 to memory access cycle (Fig. 11)  UDS HIGH to F6 (component of F1/F6)  rise (notes 1, 6 and 7)  F6 (component of F1/F6) HIGH to UDS rise | <sup>t</sup> UF6 | 20<br>40 | <br> -<br> - | -<br>- | ns<br>ns |

| SYNCHRONIZATION and BLANKING                                                                                                                   |                  |          |              |        |          |

| TCS, SAND, FS/DDA  See Fig. 12 for timing relationships and Fig. 13 for vertical sync and blanking waveforms.                                  |                  |          |              |        |          |

#### Notes to the characteristics

- 1. All pins are tested with a 150 pF load capacitor.

- 2. 16-level analogue voltage outputs.

- 3. Output voltage guaranteed when programmed for top level.

- 4. CLKO, F1/F6, VDS, FS/DDA: reference levels = 0.8 to 2.0 V. R, G, B: reference levels = 0.8 to 2.0 V with V<sub>REF</sub> = 2.7 V.

- 5. These times may momentarily be reduced to a nominal 69 ns in slave-sync mode at the moment of re-synchronization.

- 6. Reference levels = 0.8 to 2.0 V.

- 7. F6 input at 6 MHz.

- 8. Microprocessor write cycle times of less than 500 ns are permitted but often result in Wait States being generated, the precise timing of DTACK will then depend on the internal synchronization time

- 9. This timing may be infringed at the beginning and end of the memory access window.

- 10. Output voltage guaranteed when programmed for bottom level.

Fig. 3 F6 input waveform.

Fig. 4(a) Oscillator circuit for SAA5361 stand-alone sync mode and (b) equivalent circuit of crystal at resonance (see characteristics for values).

Fig. 5 Circuit arrangement giving one-of-sixteen reference voltage levels for the R, G or B analogue outputs.

Fig. 6 Video timing.

Fig. 7 Memory access timing.

Fig. 8 Timing of link-through buffers.

Fig. 9 Timing of microprocessor read from EUROM.

Fig. 10 Timing of microprocessor write to EUROM.

Fig. 11 Timing of F1/F6 to memory access cycle.

Fig. 12 Timing of synchronization and blanking outputs; all timings are nominal and assume fp  $_{\rm F6}$  = 7.2 MHz.

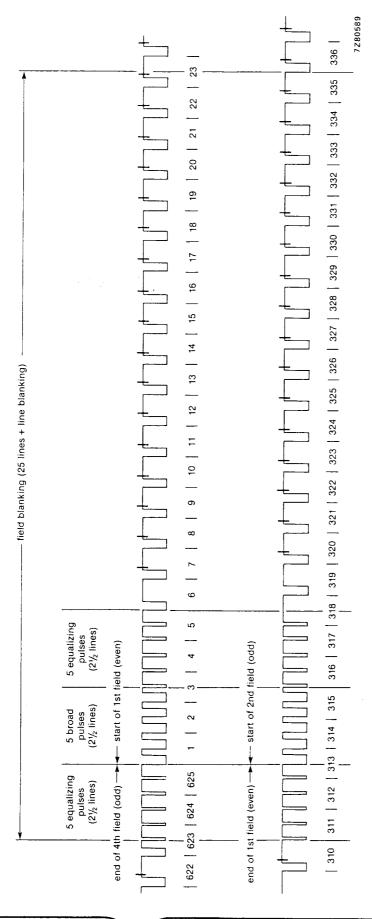

Fig. 13 Vertical synchronization and blanking waveforms; separation of broad pulses = 3.96  $\mu$ s; equalizing pulse widths = 7.88  $\mu$ s.

#### APPLICATION INFORMATION

More detailed application information is available on request

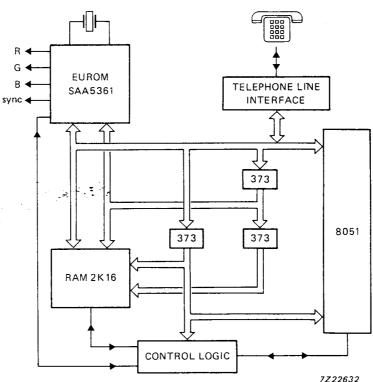

#### BASIC VIDEOTEX DECODER CONFIGURATION

A basic, practical decoder configuration is shown in Fig. 14, reference should also be made to the block diagram Fig. 1.

Fig. 14 Basic videotex decoder configuration.

Character and attribute data is fetched from the external memory, processed by the row buffer fill logic according to the stack coding scheme (in stack mode) and then fed into one half of the dual display row buffer. The data fetch process takes place during one line-flyback period (per row) and, since time is required to complete the fill, the other half of the dual row buffer is used for display. The row buffers exchange functions on alternate rows — each holds the 40 columns of 32 bits required to define explicitly every character in a row.

The addresser is used for row buffer filling and for fetching screen colours, and during the display time it is also used for addressing DRCS characters.

# **Timing**

The timing chain operates from an external 7.2 MHz clock or an on-chip fixed-frequency crystal oscillator. The basic video format is 40 characters per row, 24/25 rows per page and 10 video lines per row. EUROM will also operate with 20/21 rows per page and 12 video lines per row. The two extra lines per row are added symmetrically and contain background colour only for ROM-based alphanumeric characters. DRCS characters, block and smooth mosaics and line drawing characters occupy all 12 lines.

The display is generated to 625-line/60 Hz scanning (interlaced or non-interlaced). In addition to composite sync (pin 32) for conventional timebases, a clock output at 1.2 MHz or 7.2 MHz (pin 29) is available for driving other videotex devices, and a 14.4 MHz clock (pin 27) is available for hard-copy dot synchronization. A defined-display-area timing signal (pin 33) simplifies the application of external peripherals such as a light pen; this signal is nominally coincident with the character dot information.

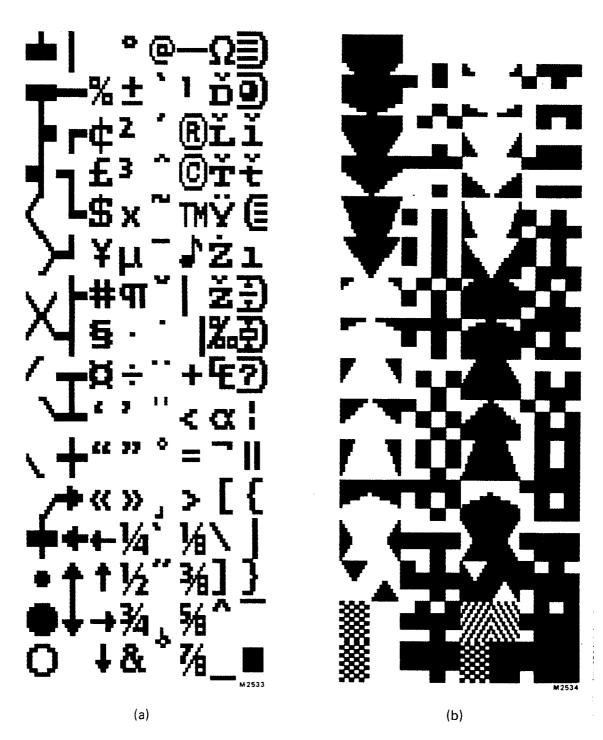

### Character generation

EUROM supports eight character tables, each of (nominally) 128 characters. Four tables are in on-chip ROM and contain fixed characters and four are stored in an external RAM. The contents of the fixed character tables (Tables 0 to 3) are shown in Figs 15 and 16.

Pğp

(a)

(b)

Fig. 15 On-chip characters: (a) Table 0; (b) Table 1.

Fig. 16 On-chip characters: (a) Table 2; (b) Table 3.

#### Character generation (continued)

The 128 most commonly used characters are contained in Table 0, these are the standard upper and lower-case letters of the Roman alphabet, numerals, punctuation and the more common accented characters. In normal text transmission, Table 0 is used most of the time. Table 1 contains other accented characters. Miscellaneous characters, mathematical symbols, the line drawing character set and accents without associated symbols are contained in Table 2. Table 3 contains the block mosaics for the basic alpha-mosaic service and also the new smooth mosaics.

The four tables stored in the external RAM (Tables 4 to 7) are used for DRCS.

#### Scroll map

The scroll map uses a 26-byte area of on-chip RAM and functions in association with the timing chain. It maps the scan row on to the fetched memory row so allowing the stored page to be displayed in any row order. For each row, a 1-byte pointer to the display memory row is stored in the scroll map. This allows scrolling without the need for data transfer to, or from, side storage.

Additional control bits are stored, allowing 1 to 25 rows to be displayed at any location on the screen.

## Colour map and digital-to-analogue converters

The colour map RAM contains thirty-two 12-bit words that are loaded by the microprocessor and read out in three 4-bit groups at pixel rate. Each group is fed to a non-linear (gamma-corrected) D-A converter. The resulting R, G and B outputs are low-impedance with peak-to-peak amplitudes controlled by the reference voltage applied at pin 21.

#### Cursor

The cursor is available in the stack mode. Its position, character code, character table, foreground colour, background colour, lining and flash attributes are all software programmable via internal register bits.

### NON-VIDEOTEX APPLICATIONS

For non-Videotex applications, the device will also support the following operating modes:

**Explicit fill mode.** An alternative 40 character/rows mode which does not use the memory compression technique of stack coding. More display memory is required but there are no limitations on the number of display attribute changes per row.

80 characters/rows mode. When operating with 80 characters per row, the available display attributes are eight foreground colours, eight (potentially different) background colours (including transparent) as well as underline and blink.

Full field DRCS mode. This mode is not mutually exclusive to the explicit fill and 80 characters/rows modes but rather the available DRCS memory is expanded so that the whole screen can be covered, thus enabling a 'bit map'. All ROM-based characters and all display attributes remain available.

#### MICROPROCESSOR and RAM BUS INTERFACE

Three types of data transfer take place at the bus interface:

- EUROM fetches data from the display memory

- The microprocessor reads from, or writes to, EUROM's internal register map

- The microprocessor accesses the display memory

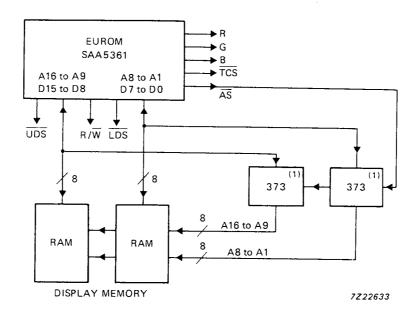

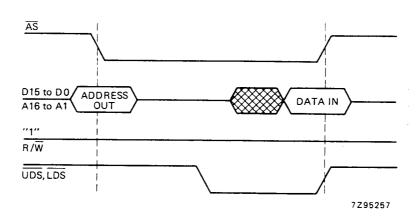

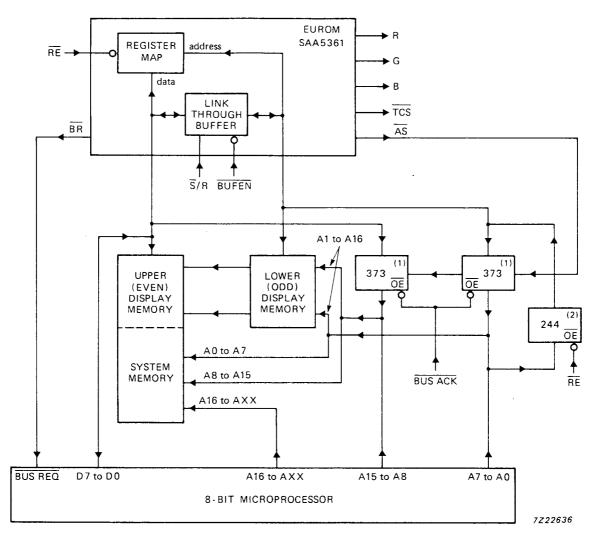

# EUROM access to display memory (Figs 17 and 18)

EUROM accesses the external display memory via a 16-bit multiplexed address and data bus with a cycle time of 417 ns. The address strobe ( $\overline{AS}$ ) signal from EUROM flags the bus cycle and writes the address into octal latches (74LS373). The display data is stored in bytes of upper (most-significant) and lower (least-significant) display information and is always fetched in pairs of bytes (upper + lower = 16 bits). The upper and lower display RAM sections are enabled simultaneously by the upper and lower data strobes (respectively  $\overline{UDS}$  and  $\overline{LDS}$ ) which are always asserted together to fetch a 16-bit word. The read/write control R/ $\overline{W}$  is included although EUROM only reads from the display memory.

#### (1) 74LS373 octal transparent latch (3-state)

Fig. 17 Simple RAM interface circuit for display memory access.

Fig. 18 Bus timing for display memory access.

#### EUROM access to display memory (continued)

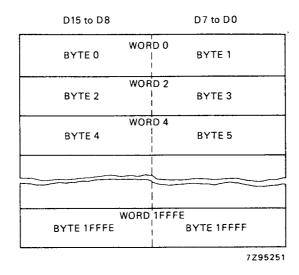

The display memory organization uses the word/byte addressing convention adopted for the SCN68000 microprocessor series. Data fetched on the 16-bit bus is considered in terms of bytes where the even numbered bytes use the upper (most-significant) part of the bus as shown in Fig. 19. The word addresses are numerically the same as the upper byte that they contain — there are no odd-numbered word addresses.

Fig. 19 Display memory word/byte organization.

#### Warning time

As EUROM is a real-time display device, it must have direct access to the display memory with priority over the microprocessor and other peripheral devices. This is achieved by EUROM issuing a bus request (BR) signal for the duration of the memory access plus a programmable advance warning time which allows the microprocessor to complete its current bus cycle.

In systems where the buses of the microprocessor and EUROM are intimately connected (connected systems),  $\overline{BR}$  may be used to suspend all microprocessor activity so that EUROM can act as a dedicated DMA controller. In systems where the two buses are separated by buffers (disconnected systems),  $\overline{BR}$  may be used either to generate an interrupt or as a direct signal. To these ends, the warning time between the assertion of  $\overline{BR}$  and the beginning of EUROM's bus activity is programmable to be between 0 and 19.2  $\mu$ s.

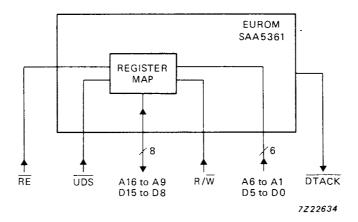

#### Microprocessor access to register map

EUROM has a set of internal registers which, when memory-mapped, behave as an 8-bit wide RAM connected to the upper part of the data bus (Fig. 20). The control signals  $\overline{\text{UDS}}$  and  $R/\overline{W}$  are reversed to become inputs and the register map is enabled by the signal  $\overline{RE}$ . Addresses are input via the lower part of the bus. A data transfer acknowledge signal ( $\overline{\text{DTACK}}$ ) indicates to the microprocessor that the data transfer is complete.

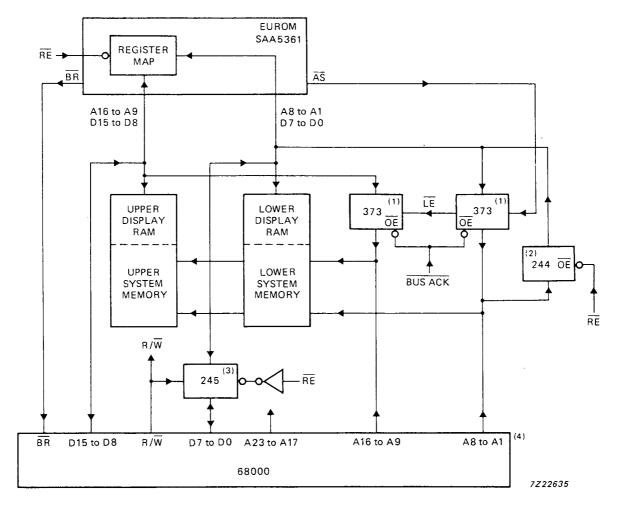

Fig. 20 Microprocessor access to register map.

The main data and address paths used in a connected 68000 interface are shown in Fig. 21. The outputs from the octal latches (74LS373) are enabled only when the 68000 has made the bus available in response to a bus request  $(\overline{BR})$ . When the register map is accessed data is transferred via the upper part of the bus and the microprocessor's low-order address is passed to EUROM via the octal buffers (74LS244). At the same time the bidirectional buffers (74LS245) disable the signals from the low order data bus of the 68000.

The buffers '244 and '245 may be omitted in a 16-bit write-only configuration where the least-significant data byte is interpreted by EUROM as an address. Here it will generally be necessary for the microprocessor to hold a (readable) 'master copy' of EUROM's scroll map contents at a location in its main memory.

#### 8-bit microprocessors

Although the control bus is optimised for the SCN68000 16-bit microprocessor unit, EUROM will operate with a number of widely differing industry-standard 8, 16 or more-bit microprocessors or microcontrollers (e.g. SCN68008, MAB8051). The interfacing of 8-bit microprocessors to the 16-bit wide display memory is made simple by EUROM's on-chip link-through buffer which provides the microprocessor with bidirectional access to the lower (odd) half of the memory. The link-through buffer is enabled by the buffer-enable signal  $\overline{\text{BUFEN}}$ , and the send/receive direction is controlled by the signal  $\overline{\text{S}/\text{R}}$ .

The main data and address paths used in a connected 8-bit microprocessor system are shown in Fig. 22. The interface is similar to that of the 16-bit system but here the display memory does not receive A0 as an address, rather A0 is used as the major enabling signal for BUFEN (enables when HIGH).

- (1) 74LS373 octal transparent latch (3-state)

- (2) 74LS244 octal buffer (3-state)

- (3) 74LS245 octal bus transceiver (3-state)

- (4) SCN68000 microprocessor unit

Fig. 21 Connected 16-bit microprocessor system.

- (1) 74LS373 octal transparent latch (3-state)

- (2) 74LS244 octal buffer (3-state)

Fig. 22 Connected 8-bit microprocessor system.

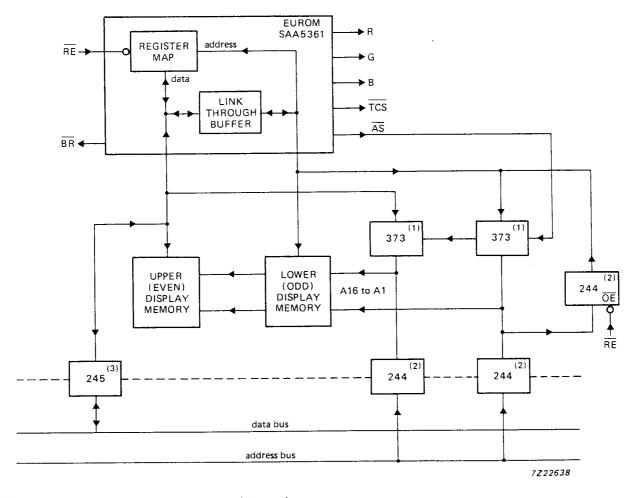

# Disconnected systems

For many applications it may be desirable to disconnect EUROM and the display memory from the microprocessor and its ROM, RAM and other peripherals by using isolating buffers as shown in Fig. 23. The two parts of the system then operate independently and communicate only when the microprocessor accesses EUROM's register map or the display memory.

- (1) 74LS373 octal transparent latch (3-state)

- (2) 74LS244 octal buffer (3-state)

- (3) 75LS245 octal bus transceiver (3-state)

Fig. 23 Disconnected 8-bit system.

#### Synchronization

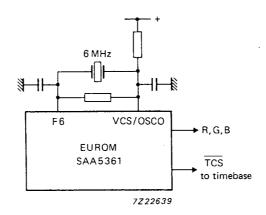

#### Stand-alone mode

As a stand-alone device (e.g. in terminal applications) EUROM can output a composite sync signal (TCS) to the display timebase IC or to a monitor. Timing is obtained from a 7.2 MHz on-chip oscillator using an external crystal as shown in Fig. 24.

Fig. 24 Stand-alone synchronization mode.

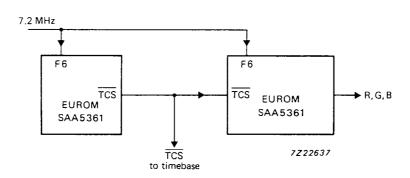

# Simple-slave

In the simple-slave mode EUROM synchronizes directly to another device, such as to the TCS signal from another EUROM as shown in Fig. 25. EUROM's horizontal counter is reset by the falling edge of TCS. A dead time of 208 ns is built in to avoid resetting the counter at every tv line and so prevents screen jitter.

Field synchronization is made using EUROM's internal field sync separator.

Fig. 25 Simple-slave (direct sync) mode.

# Synchronization (continued)

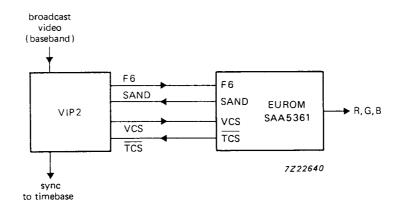

#### Phase-locked slave

The phase-locked slave (indirect sync) mode is shown in Fig. 26. Part of a VIP2 forms alu. When EUROM is active, its horizontal counter forms part of the phase control loop — a horizontal reference is fed back to the VIP2 from the SAND output and a vertical reference is generated by feeding separated composite sync to EUROM's field sync separator via the VCS input. In the phase-locked slave mode, the display derived from EUROM can sync with that from a tv source or a local VLP player, thus giving picture-in-text display possibilities.

Fig. 26 Phase-locked slave (indirect sync) mode.